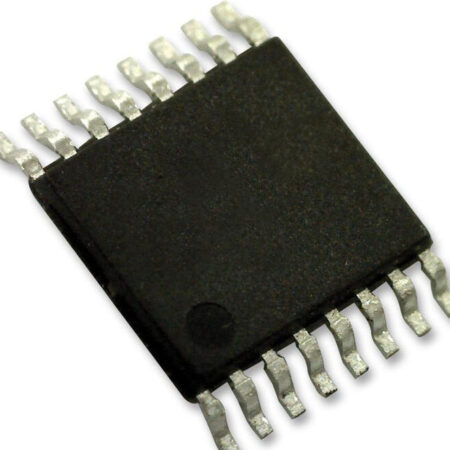

GL852G is Genesys Logic’s premium 4-port Hub solution which fully complies with Universal Serial Bus Specification Revision 2.0. GL852G implements multiple TT* (Note1) architecture that provide dedicated TT* to each downstream (DS) ports, which guarantee Full-Speed(FS) data passing bandwidth when multiple FS device perform heavy loading operations. The controller inherits Genesys Logic’s cutting edge technology on cost and power efficient serial interface design. GL852G has proven compatibility, lower power consumption figure and better cost structure above all USB2.0 hub solutions worldwide.

GL852G implements multiple hub configuration features onto internal mask ROM, which traditionally requires one external EEPROM. The microprocessor detects general purpose I/O (GPIO) status during the initial stage to configure hub settings such as (1) number of DSport, (2) declare of compound device (3) gang/individual mode selection…etc. External EEPROM can be removed if no vendor specified PID/VID or product string is required for the application.

GL852G supports four package types, summarized as below table. LQFP48 package provides full hub features such as (1) two-color (green/amber) status LEDs for each DS ports, (2) Individual/Gang mode power management scheme that indicates DS port over-current events. (3) Number of DS ports setting configured by GPIO setting (4) non-removable declaration configured by GPIO setting (5) Support both 93C46 and 24C02 EEPROM (6) power switch polarity selections…etc. QFN28 package support only partial hub features but provide smaller footprint (5x5mm) that targets space limited PCB layout environments such as embedded system or UMPC/MID applications.

Reviews

There are no reviews yet.